# PHY 305F – ELECTRONICS LABORATORY I Fall Semester 2003

# EXPERIMENT 4 DIGITAL DEVICES, GATES, AND FLIP-FLOPS Lab notebook is due at 1 PM in MP238 on November 3

## LEARNING OBJECTIVES:

- (1) To learn the basic properties of several digital gates.

- (2) To learn the basic properties of several digital flip-flops.

- (3) To become familiar with the use of a LED with driver to provide a visual display.

- (4) To use NAND and NOR gates to make flip-flops, and to investigate one flip-flop chip.

- (5) To learn what a shift register does.

- (6) To gain practice in working out for yourself the details of what wiring and measurements need to be done in order to investigate the properties of a given device.

#### **REFERENCES**:

- D. Lancaster, TTL Cookbook.

- D. Lancaster, CMOS Cookbook.

A.J. Diefenderfer and B.E. Holton, Principles of Electronic Instrumentation, 3rd Edition, Chapters 11 & 12.

- P. Horowitz and W. Hill, <u>The Art of Electronics</u>, 2<sup>nd</sup> Edition, Chapters 8 & 9.

- L.R. Fortney, Principles of Electronics, Analogue and Digital, Chapter 9.

Senturia and Wedlock, Electronic Circuits and Applications, Chapter 16.

R.E. Simpson, Introductory Electronics for Scientists and Engineers, 2<sup>nd</sup> Edition, Chapter 13, Appendix H.

G. Rizzoni, <u>Principles and Applications of Electrical Engineering</u>, 3<sup>rd</sup> Edition, Chapters 13 & 14.

Any of the various manuals on TTL devices in the lab.

#### WHAT TO DO:

*NOTE 1: A number of TTL logical gates are available in the cupboard. In particular, of relevance to this experiment are:*

| •                                            | Inverter                   | 7404 |

|----------------------------------------------|----------------------------|------|

| •                                            | 2-input NAND gate          | 7400 |

| •                                            | 2-input NOR gate           | 7402 |

| •                                            | 4-input NAND gate          | 7420 |

| •                                            | 4-input AND/OR invert gate | 7451 |

| •                                            | 2-input XOR                | 7486 |

| ٠                                            | Schmitt trigger (invert)   | 7414 |

| There is also a CMOS 2-input NOR gate, 4001. |                            |      |

You might also wish to look at other gates. In this experiment, with the exception of the 4001, all the gates you use belong to the TTL logic family.

NOTE 2: You will be wiring up several devices on the same proto-board. Be sure to be systematic in setting up your power and ground buses. Also, be sure to use despiking capacitors across the power rails. You will want to maintain throughout, for indication of the logical state of the gates, the light display you use in part 1, using a 7406 (or 7416) and an LED. However, you will probably need 3 to 5 lights.

*NOTE 3: This experiment is very open-ended, particularly in parts 3 and 5. It is intended to be done in a limited time, so choose carefully and systematically the tasks that you wish to pursue.*

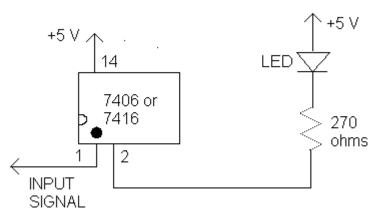

(1) Hook-up a LED to a 7406 TTL driver as shown in the figure below. (Note: From the TTL Cookbook, you will see that the 7406 has six units in one package. You will be using only one of these units.) Check that an input of 0 V (low) turns the light off and an input of +5 V (high) turns the light on. (Note that in TTL, a disconnected input is equivalent to the input set at "high").

- (2) <u>Very briefly</u> investigate the transfer characteristics (output volts vs. input volts) of a TTL gate by looking at the 7404 inverter. Also investigate the transfer characteristic of a CMOS gate using the 4001 two-input NOR gate with the two inputs tied together. Note what happens to both types of gate when the input is left open-circuited.

- (3) Investigate the logical function of one or more of the two or four input gates mentioned above, constructing a truth table for each gate you investigate.

- (4) Investigate the transfer characteristic of the 7414 Schmitt trigger.

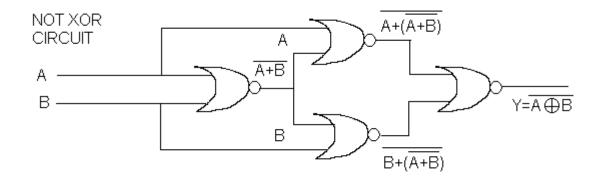

- (5) Define one or two simple logical decisions you wish to have modelled, and connect up combinations of the gates mentioned above to perform this logic. Suggestions could include a HALF ADDER, an XOR, or some other decision such as an example from a textbook. The case of the NOT XOR is illustrated in the figure below. In this case, the implementation is by four two-input NAND gates. It may also be noted that the XOR function is obtainable on the 7486 chip. Note that a FULL ADDER function is also obtainable on a single chip, the 7482 (two-bit) or the 7483 (four-bit).

- (6) Construct an S-R (set-reset) or an  $\overline{S} \overline{R}$  flip-flop from two NAND gates or from two NOR gates as described in Fortney pages 385-387 or Simpson pages 599-602. Familiarize yourself with the behaviour of the S-R flip-flop and obtain a truth table for its operation. Why is one set of input states never used?

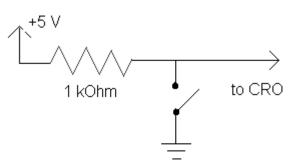

- (7) Construct a bouncy mechanical switch as shown at the right. (Note: many mechanical switches are bouncy – this means that they generate a very fast sequence of on/off due to the nature of the mechanical contacts.) Sketch v<sub>out</sub> vs. t as the switch is closed or opened. What is the approximate time for the bounce? (You will most easily see the signal using the digital storage CRO.)

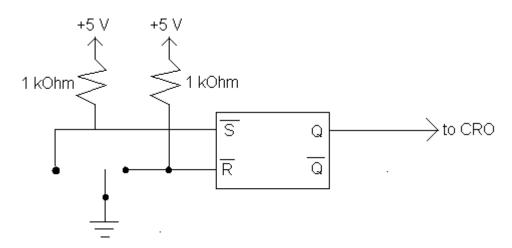

(8) Construct a debounced switch using the S-R flip-flop, as shown below. Again observe the pulses on the CRO. (Your connections will have to change depending on whether you use an S-R or an  $\overline{S} - \overline{R}$  flip-flop.)

(9) With reference to Fortney pages 390-395, or Simpson pages 612-615, or the TTL Cookbook pages 193-196, observe the function of the 7476 J-K flip-flop, both in asynchronous and clocked operation. Use the "Pulse Out" output of the Wavetek Function Generator for the clock pulse.

(10) Shift registers are described in Fortney pages 400-401, or Simpson pages 627-632, or the TTL Cookbook pages 206-207 and 258-262. They can be constructed from J-K flip-flops strung together; shift register chips are also available. Construct and test the states of a shift register using either four J-K flip-flops or a 7495 shift register chip.

## COMMENTS:

- (1) It will be important for you to think out carefully how you use your board to best allow you to set up the chips and make your measurements.

- (2) In making your observations, the CRO is a likely instrument for visually showing you what your circuits are doing, although meters are a good way to see voltages quantitatively. However, in general, you will have to decide which voltage detecting devices you will use. For instance, if you are merely trying to indicate whether a device is in a high or low state, it may be both convenient and colourful to use the light display to indicate a high or low state of a line. To put it more strongly, the states of the system in parts 3, 5, 6, 9, and 10 are easily seen using the lights. Any other method will make your life unnecessarily complicated.

- (3) Note that TTL chips are powered between +5 V and ground. Do not use higher supply voltages.

- (4) Note that the descriptions given of the logical component assume positive logic, with a 0 state being a low state (close to 0 V), and a 1 state being a high state (close to 4 or 5 V).

- (5) In writing up your observations, be sure to explain what you see in terms of what the references and/or lecture notes predict, and to explain the functioning of logical circuits. In particular, note and comment on all idiosyncracies of the circuits that you observe.